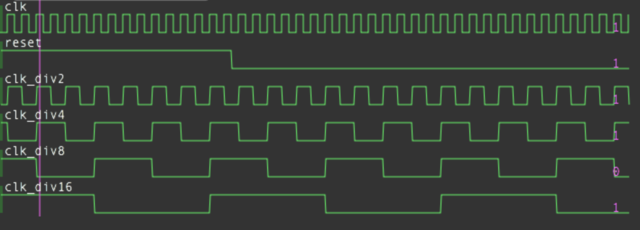

Divizor cu 16

Sari la navigare

Sari la căutare

/*

Un exemplu de divizor cu 16 care folosește metoda flip-flop-urilor în cascadă

*/

module clock_divider(

input clk,

input reset,

output reg clk_div2,

output reg clk_div4,

output reg clk_div8,

output reg clk_div16

);

always @(posedge clk). // la fiecare front pozitiv de tact...

clk_div2 <= ~clk_div2; // semnalul clk_div2 trece în low la fiecare al doilea tact = divizare cu 2

always @(posedge clk_div2) // etc, pe baza logicii de mai sus

clk_div4 <= ~clk_div4;

always @(posedge clk_div4)

clk_div8 <= ~clk_div8;

always @(posedge clk_div8)

clk_div16 <= ~clk_div16;

endmodule