Sincronizare verticală pentru semnal video: Diferență între versiuni

Sari la navigare

Sari la căutare

Fără descriere a modificării |

Fără descriere a modificării |

||

| Linia 1: | Linia 1: | ||

Comentariile vin imediat. ;) Pagină în lucru. | |||

<syntaxhighlight lang="verilog"> | <syntaxhighlight lang="verilog"> | ||

| Linia 106: | Linia 107: | ||

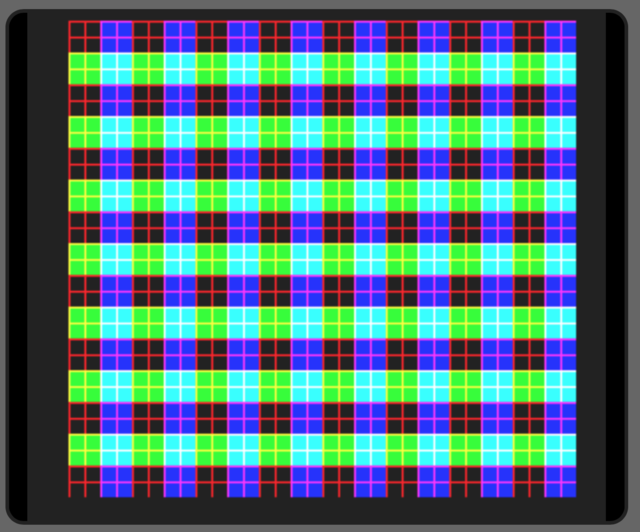

[[Fișier:Vertical sync, video pattern.png|none|640px|Vertical sync, video pattern]] | [[Fișier:Vertical sync, video pattern.png|none|640px|Vertical sync, video pattern]] | ||

==Cărți== | |||

* [https://plan.seek.intel.com/PSG_WW_NC_LPCD_FR_2018_FPGAforDummiesbook FPGAs For Dummies] | |||

Versiunea curentă din 1 februarie 2020 13:51

Comentariile vin imediat. ;) Pagină în lucru.

`ifndef HVSYNC_GENERATOR_H

`define HVSYNC_GENERATOR_H

/*

Video sync generator, used to drive a simulated CRT.

To use:

- Wire the hsync and vsync signals to top level outputs

- Add a 3-bit (or more) "rgb" output to the top level

*/

module hvsync_generator(clk, reset, hsync, vsync, display_on, hpos, vpos);

input clk;

input reset;

output reg hsync, vsync;

output display_on;

output reg [8:0] hpos;

output reg [8:0] vpos;

// declarations for TV-simulator sync parameters

// horizontal constants

parameter H_DISPLAY = 256; // horizontal display width

parameter H_BACK = 23; // horizontal left border (back porch)

parameter H_FRONT = 7; // horizontal right border (front porch)

parameter H_SYNC = 23; // horizontal sync width

// vertical constants

parameter V_DISPLAY = 240; // vertical display height

parameter V_TOP = 5; // vertical top border

parameter V_BOTTOM = 14; // vertical bottom border

parameter V_SYNC = 3; // vertical sync # lines

// derived constants

parameter H_SYNC_START = H_DISPLAY + H_FRONT;

parameter H_SYNC_END = H_DISPLAY + H_FRONT + H_SYNC - 1;

parameter H_MAX = H_DISPLAY + H_BACK + H_FRONT + H_SYNC - 1;

parameter V_SYNC_START = V_DISPLAY + V_BOTTOM;

parameter V_SYNC_END = V_DISPLAY + V_BOTTOM + V_SYNC - 1;

parameter V_MAX = V_DISPLAY + V_TOP + V_BOTTOM + V_SYNC - 1;

wire hmaxxed = (hpos == H_MAX) || reset; // set when hpos is maximum

wire vmaxxed = (vpos == V_MAX) || reset; // set when vpos is maximum

// horizontal position counter

always @(posedge clk)

begin

hsync <= (hpos>=H_SYNC_START && hpos<=H_SYNC_END);

if(hmaxxed)

hpos <= 0;

else

hpos <= hpos + 1;

end

// vertical position counter

always @(posedge clk)

begin

vsync <= (vpos>=V_SYNC_START && vpos<=V_SYNC_END);

if(hmaxxed)

if (vmaxxed)

vpos <= 0;

else

vpos <= vpos + 1;

end

// display_on is set when beam is in "safe" visible frame

assign display_on = (hpos<H_DISPLAY) && (vpos<V_DISPLAY);

endmodule

`endif

`include "hvsync_generator.v"

/*

A simple test pattern using the hvsync_generator module.

*/

module test_hvsync_top(clk, reset, hsync, vsync, rgb);

input clk, reset;

output hsync, vsync;

output [2:0] rgb;

wire display_on;

wire [8:0] hpos;

wire [8:0] vpos;

hvsync_generator hvsync_gen(

.clk(clk),

.reset(0),

.hsync(hsync),

.vsync(vsync),

.display_on(display_on),

.hpos(hpos),

.vpos(vpos)

);

wire r = display_on && (((hpos&7)==0) || ((vpos&7)==0));

wire g = display_on && vpos[4];

wire b = display_on && hpos[4];

assign rgb = {b,g,r};

endmodule